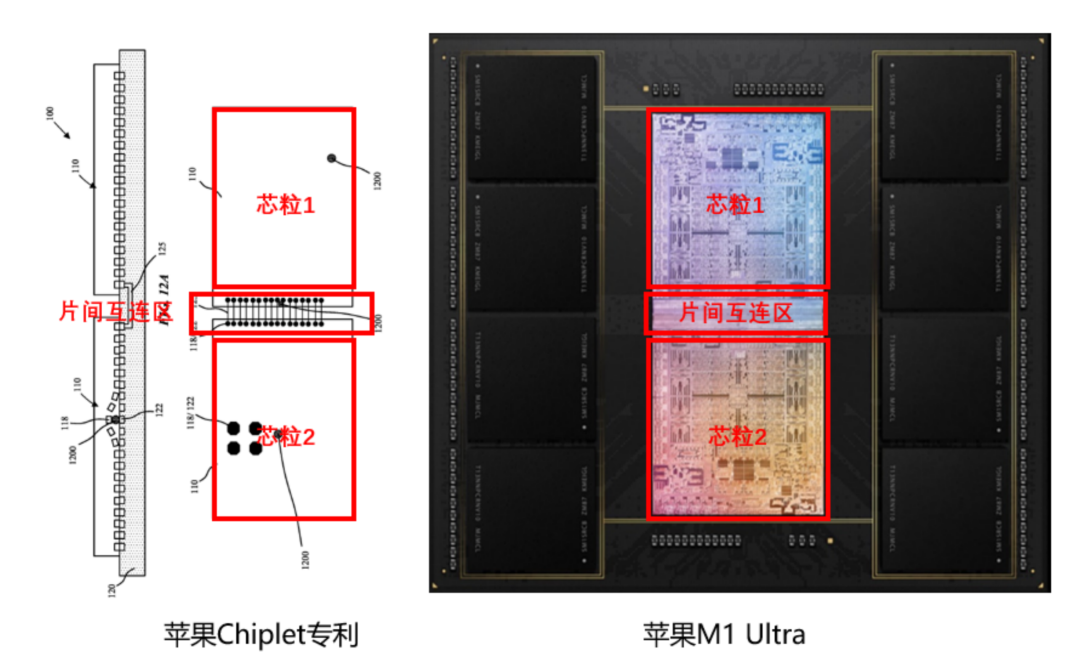

▲苹果Chiplet专利与M1 Ultra芯片(参考专利US 20220013504A1)

值得注意的是,拥有顶级芯片设计水平的苹果,并未出现在UCIe标准的首发成员名单中,其M1 Ultra芯片的实现方式,也与UCIe不同,反倒与我国正在推进的chiplet标准在目的和功能上有些类似。标准的制定对于生态的扩张至为关键,但多位业内专家或资深人士告诉芯东西,UCIe标准对国内产业的价值还很模糊,尤其在全球科技“武器化”和美国政府提防中国科技崛起的地缘冲突背景下,这个新标准预计很难为国内厂商提供助力。芯东西获悉,国内chiplet标准草案现已制订完毕,即将进入征求意见阶段,预计第一季度挂网公示和意见征集,第二季度完成技术验证计划制订,年底前完成技术验证,并完成标准文本的确定,进行初版标准的发布工作,首个版本发布即可用。那么,国内外标准存在哪些异同?这些标准的建立会怎样影响后摩尔时代芯片的发展格局?推进此类标准的建设,还需突破哪些障碍?围绕这些问题,近日,芯东西与无锡芯光互连技术研究院院长、无锡芯光集成电路互连技术产业服务中心主任、中国计算机互连技术联盟秘书长、中科院计算所研究员郝沁汾进行深入交流,解读chiplet标准建设背后的痛点、趋势与隐忧。芯谋研究分析师张先扬亦为本文贡献了有价值的行业观点。

▲无锡芯光互连技术研究院院长、无锡芯光集成电路互连技术产业服务中心主任、中国计算机互连技术联盟秘书长、中科院计算所研究员郝沁汾

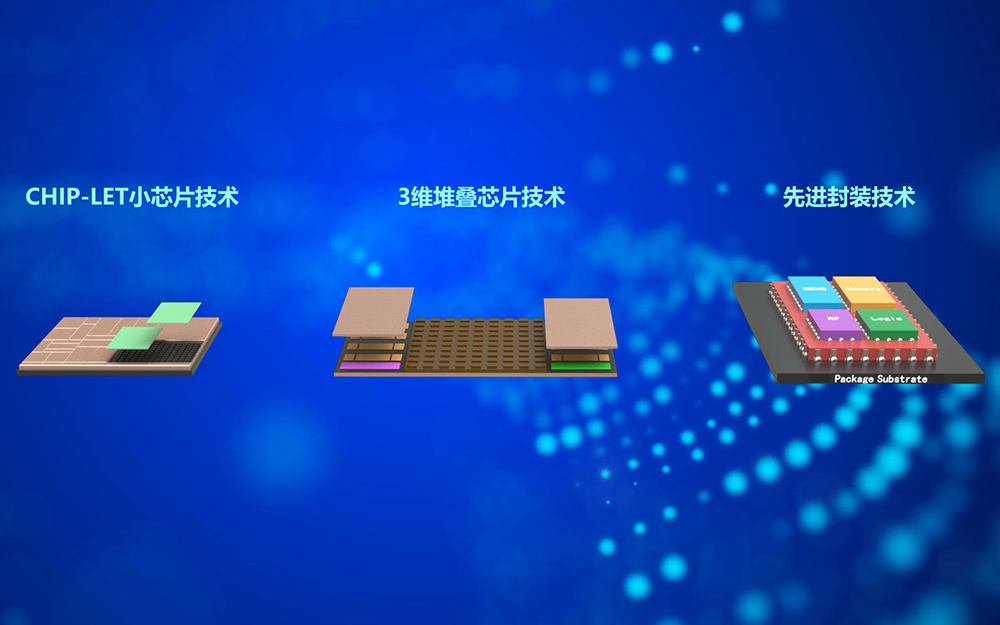

▲部分集成电路互连技术种类示意图

2015年,Marvell创始人周秀文在ISSCC 2015上提出MoChi(模块化芯片)架构概念。随后,AMD率先将chiplet应用于商业产品中。相比之下,英特尔切入这一技术方向的时间稍晚。2020年1月,英特尔加入由Linux基金会主办的美国CHIPS联盟,并免费提供了AIB互连总线接口许可,以支持chiplet生态系统的建设。但由于需使用英特尔自家的先进封装技术EMIB,AIB标准未能广泛普及。今年3月,英特尔又牵头发起一项chiplet新标准,即开篇提到的UCIe标准。

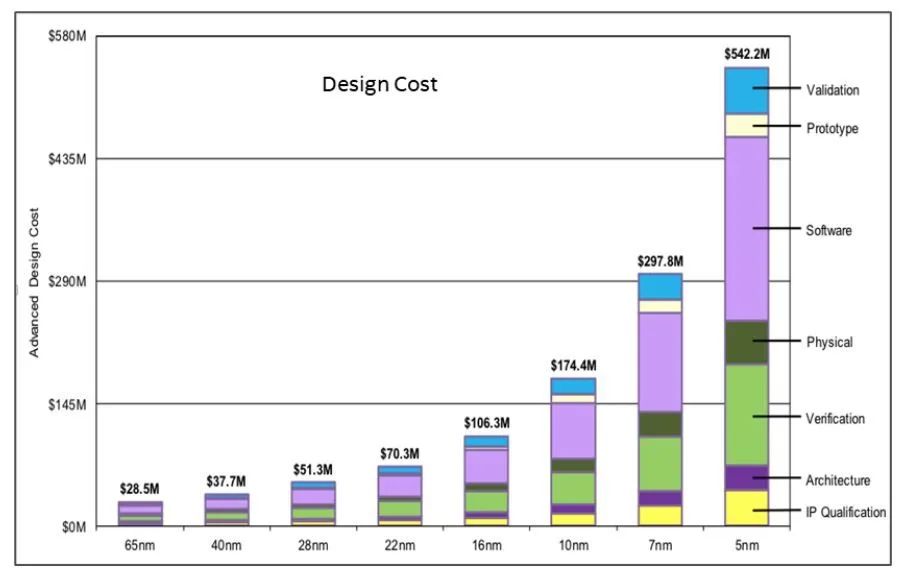

▲随着先进制程演进,芯片设计成本飙升

相比单芯片设计,基于chiplet设计的芯片,可以进一步提升良率,降低成本,同时性能更强。一颗芯片上有不同功能的模块组件,如果全用最先进的技术节点来制造,成本会非常高。而多颗小芯片封装在一起,通过让不同功能的芯片模块分别选用合适的制程工艺,不仅可在技术方面实现各功能的最优化,合理利用先进工艺提升那些能够获益的芯片内容,也能进一步节约生产成本,提升所设计芯片的总体性价比。除此之外,芯片面积越大,良品率越低。比如150mm²芯片的良品率有80%,到700mm²已经低至30%。Chiplet采用多颗小芯片组合的思路,以更小的裸片提升总体良率,可以带来更高的硅利用率和产能。因此,芯片业已经不再只关注单裸片芯片,而是开始将多个裸片组成的单个芯片集成到系统中,并有越来越多的芯片公司投入相关研发。但随着基于chiplet的芯片品类逐渐多样,缺乏标准的问题逐渐变得棘手。

▲UCIe联盟首批成员名单

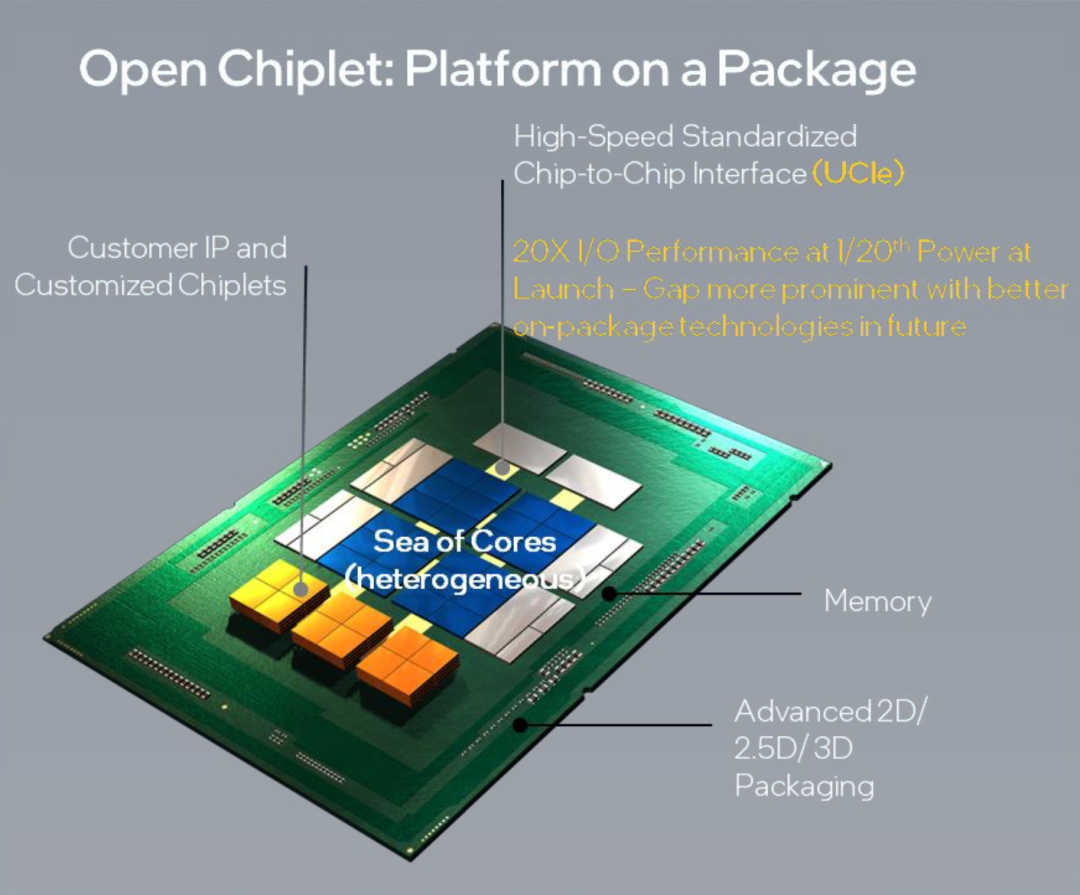

在郝沁汾看来,英特尔牵头这些标准的核心动力,是维护和丰富其生态系统的完整性。UCIe标准明确提出支持CXL和PCIe协议,而这两个互连协议均由英特尔提出和创建。例如,PCIe是x86系统主要的IO总线标准,所有IO设备必须支持PCIe才能和X86 CPU相连。由于目前很多加速器芯片的计算能力,已经可以和主CPU相提并论,因此CXL在IO模式基础上,又新增了CXL.mem和CXL.cache的模式,以适应技术形势的发展。值得注意的是,UCIe联盟的初始成员名单中,没有苹果、英伟达等芯片圈知名“狠角色”,也完全没有中国大陆厂商的身影。英伟达可能是因为其业务高毛利,对成本不敏感,暂时对chiplet这种设计方式不太感兴趣,再加上英伟达有自己的片间互连协议NVLink,与英特尔对数据中心场景的一些期望不一致,因此支持UCIe与否不是必须为之。而苹果上周最新发布的电脑芯片M1 Ultra,已是在chiplet方向上的一次成功尝试。至于面向国内芯片企业,有一个问题值得商榷:UCIe标准的“开放”,究竟是何种程度的开放?

▲UCIe的介绍是一个开放的行业标准互连

“我们认为的开放,应该是从标准的协议到参考实现都是开放的,但是我们看到英特尔所标榜的这些标准,从PCIe到CXL、AIB和UCIe,实现参考设计所需要的技术细节,你都在标准协议中找不到的。”郝沁汾曾向另一家更早开展chiplet互连标准制定的美国组织ODSA写邮件询问,还托以前的同事去交流,结果对方明确告知,该标准中很多涉及实现的技术细节是不能对中国开放的。这与美国政府的“视同出口”规定有关,美国企业假如没有申请出口许可就将技术输向海外,哪怕只是在标准会议中的技术探讨,都属于违规。因此,在中美关系仍较为紧张的情况下,美国技术联盟如果贸然将大陆厂商拉进去,会承担法规方面的风险。“标准有国界”的警钟三年前就敲响过。2019年5月,美国商务部宣布将华为列入实体清单,随后PCIe组织PCI-SIG曾短暂地停掉华为的会员资格。再结合近期的俄乌战事,可以看到科技已经“武器化”,假如哪天美国政府再次升级技术出口管制措施,依赖国际标准的国内企业可能要吃些苦头。在芯谋研究分析师张先扬看来,UCIe的出现,代表着全球半导体产业已经进入到成熟的产业阶段。但UCIe是否具有持续的市场前景,主要看未来chiplet与高度集成的单片芯片是否会形成差异化的市场结构,这一点很像大家在讨论的ASIC和FPGA谁是最终归属的问题。此外,UCIe产业联盟成员基本可形成一个小的产业生态闭环,这将进一步提高各产业环节的集中度,并巩固了龙头优势,是否会真正利好半导体产业的发展也是存疑的。“尤其需要注意到英特尔在美国半导体产业中扮演的敏感角色,在此特定背景下,我们不希望看到UCIe会成为政治化的工具。”他告诉芯东西。张先扬认为,国内方面,我们要继续走好自己的路,在加速国产化替代的同时,做好应对一切冲击的准备,UCIe提供了一种可参考的产业平台机制,我们亦可以通过组建内部产业联盟的方式来优化产业分工,进一步加快国内产业发展,提高国内半导体产业对于冲击的耐受力。这也是郝沁汾决定另起炉灶,在国内构建一套原生chiplet标准的初衷。

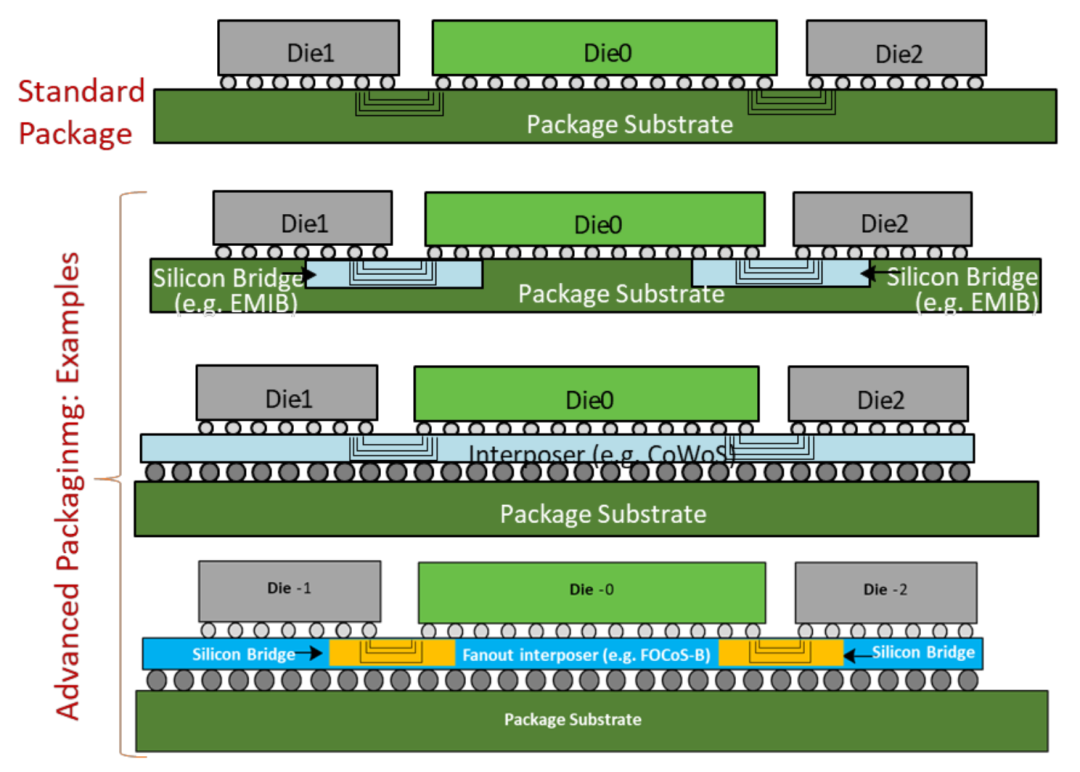

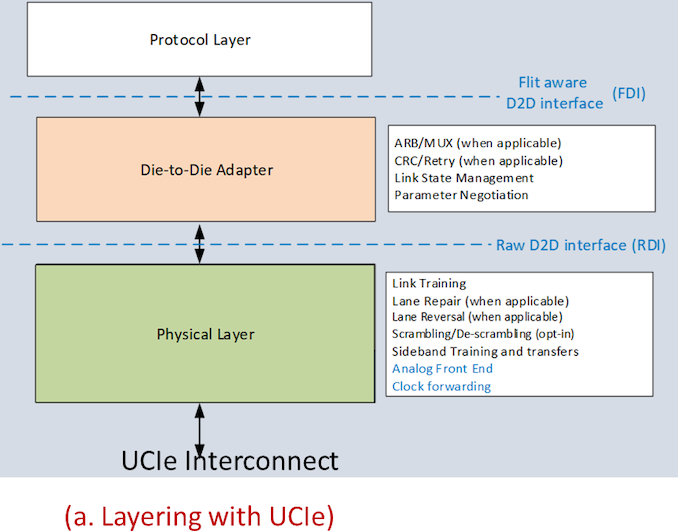

▲UCIe支持的封装方式

在郝沁汾看来,先进制程停滞背景下,chiplet面临着很好的机会,但我国面临的最现实问题,不是先进制程停滞,而是先进制程被禁运了怎么办?战略风险在于,倘若UCIe支持的三种先进封装技术被禁运,大陆厂商想用UCIe协议,只能采用标准封装的方式。而采用标准封装方式的chiplet间互连带宽,仅有采用先进封装带宽的1/6,性能大幅缩水。在标准组成上,UCIe主要由D2D适配层、物理层(含封装)组成,图中虚线以上是既有协议,CXL或PCIe。我国的《小芯片接口总线技术要求》也有类似的组成,由链路适配层、物理层及封装组成。

▲UCIe分层协议的组成

两个标准的关键区别之一在于,UCIe在D2D组成的芯片中,加入了一种叫retimer的功能芯片定义,它负责把信号由并行转成串行,然后以更高速度传送到较远的地方。郝沁汾谈道,这个目的主要是为了实现英特尔自身在数据中心中CPU和内存解耦、资源池化方案。国内《小芯片接口总线技术要求》则不包括这部分内容,而是一个纯粹的D2D互连标准。郝沁汾认为,我国的标准更加符合国情。比如在物理层,国内chiplet标准同时支持单端信号和差分信号,单端的信号是一根线,差分信号是一对线,可以把信号传的更远一点。通过chiplet将两个芯片互连,只要支持差分信号,就能使国内某些加速器芯片厂商实现将相同的芯片通过差分信号接口相连,以拓展总体性能的目的。这种先用成熟工艺做出小芯片、再用先进封装技术把它们拼在一起的方式更加廉价经济,可替代采用7nm、5nm先进制程工艺生产芯片的昂贵方案。上周苹果最新推出的最强电脑芯片M1 Ultra,其实现方式与国内的chiplet标准更为类似。而UCIe只支持通过单端信号实现D2D互连,与国内厂商的现阶段诉求不一致,实用性欠佳。郝沁汾告诉芯东西,国内chiplet标准既支持像台积电CoWoS等先进封装方式,也支持国内先进封装方法的最新积累,这样国内企业万一被施加技术限制,至少还有个备用方案,而不至于措手不及。*博客内容为网友个人发布,仅代表博主个人观点,如有侵权请联系工作人员删除。